# HEWLETT-PACKARD JOURNA MAY 1983 -10 -20 75 -30 O G BO73A SYNTHESIZED SIGNAL GENERATOR 9 8 5 4 3 2 1 0 AUTO PEAE

# HEWLETT·PACKARDJOURNAL

Technical Information from the Laboratories of Hewlett-Packard Company

# MAY 1983 Volume 34 • Number 5

# **Contents:**

**3 2-to-26.5-GHz Synthesized Signal Generator Has Internally Leveled Pulse Modulation, by William W. Heinz and Paul A. Zander** Other features are microcomputer control, front-panel data entry, digital sweep, and internal diagnostic capability.

**Sample-and-Hold Leveling System, by Ronald K. Larson** A logarithmic amplifier in the feedback loop reduces the effects of loop-gain variations.

**A Wideband YIG-Tuned Multiplier and Pulsed Signal Generation System, by Ronald K. Larson and Lawrence A. Stark** This system enhances output power and frequency range and reduces pulse rise time for HP's latest synthesized signal generator.

**Autopeaking, by Paul A. Zander** A small amount of hardware and some microprocessor code adjusts a YIG-tuned multiplier to the center of its passband.

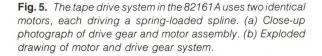

**Compact Digital Cassette Drive for Low-Cost Mass Storage, by William A. Buskirk, Charles W. Gilson, and David J. Shelley** This portable, battery-operated unit provides low-cost data and program storage for HP-IL systems.

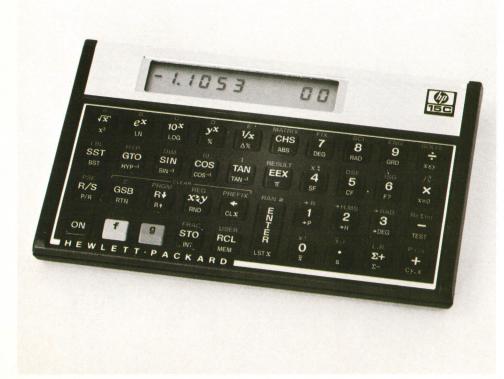

Scientific Pocket Calculator Extends Range of Built-In Functions, by Eric A. Evett, Paul J. McClellan, and Joseph P. Tanzini Complex number and matrix computations, integration, and equation solving are only a few of this programmable calculator's capabilities.

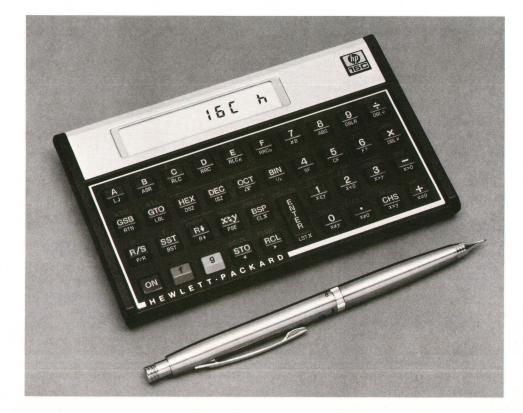

**A Pocket Calculator for Computer Science Professionals, by Eric A. Evett** This new programmable calculator works with Boolean algebra, converts number bases, and manipulates bits. It also does arithmetic.

# In this Issue:

For the design, production, and maintenance of radar and communications systems, sources of pulsed high-frequency signals are always in demand. The more versatile the source, the more jobs it can do and the more cost-effective it is (they're never cheap). Desirable attributes include broad frequency coverage, a good mix of modulation capabilities for simulating real-world signals, accurate output power controllable over a wide range, low noise, programmability for use in automatic systems, and of course, reliability.

This month's cover subject, the HP 8673A Synthesized Signal Generator, is designed to satisfy the needs of some pretty demanding applications. In radar receiver testing, for

example, it can simulate the radar pulses picked up by an antenna, even mimicking the variation in the strength of the pulses as the antenna rotates past a target. Its capabilities come partly from microprocessor control and partly from advanced microwave circuit design. The full design story is on pages 3 to 16. The cover shows the classic pulse-train spectrum of the pulsed microwave output from the 8673A.

A few issues ago, the subject of several of our articles was the Hewlett-Packard Interface Loop, or HP-IL, a method of interconnecting battery-powered computers, peripherals, and instruments to form portable systems that can go into the field to make measurements and record data. Currently, there's just one battery-powered HP-IL peripheral for recording data, and that's the HP 82161A Digital Cassette Drive. This book-sized device can store and retrieve 131,000 characters of data using a matchbox-sized magnetic tape cartridge. Because of its intended use, it has to be light and rugged and use little power. In the article on page 17, its designers tell us how they met these goals.

The articles on pages 25 and 36 describe a pair of unusually capable programmable pocket calculators. One of them, the HP-15C, is for engineers, scientists, and mathematicians. It has a truly remarkable repertoire of mathematical functions that one would normally expect to need a computer for. Now, if you need matrix arithmetic, complex-number operations, equation solving, or numerical integration, you can just reach in your pocket. It's a vivid demonstration, I think, of what integrated circuit and computer technologies are doing for us.

The other calculator, the HP-16C, is for computer programmers and designers of digital circuits. Besides the usual arithmetic functions, it performs many of the basic operations of digital circuits and computers. For example, it can shift, rotate, mask, set, clear, test, and count the bits in a digital word. It has the fundamental combinational logic functions (OR, AND, NOT, and XOR) and it manipulates numbers in four different bases—hexadecimal, decimal, octal, and binary. With this little marvel, the professional can simulate a computer algorithm or logic circuit to see if it works—another computer-sized job cut down to pocket size.

-R. P. Dolan

# 2-to-26.5-GHz Synthesized Signal Generator Has Internally Leveled Pulse Modulation

This second-generation instrument features microprocessor control, sophisticated sweep capabilities, programmability, and enhanced serviceability.

# by William W. Heinz and Paul A. Zander

**B** ROADBAND, synthesized microwave signal generators offer the stability, frequency accuracy, and spectral purity of a synthesizer together with the level accuracy and AM and FM capabilities of a signal generator. They have found numerous applications in communications and radar testing and simulation. Programmability has generated widespread use of these instruments in automatic test systems.

Since the introduction of the HP 8672A Synthesized Signal Generator in 1976,<sup>1,2,3</sup> increasing user sophistication and demands for performance enhancements have led to the next generation in this instrument family. The new 8673A Synthesized Signal Generator (Fig. 1) covers the 2-to-26.5-GHz frequency range and features internally leveled pulse modulation capability. The addition of microcomputer control provides keyboard operation, data entry from the front panel, digital sweep capability, and many other features. Calibrated output levels from -100dBm to +8 dBm are available over the 2-to-18-GHz frequency range. Maximum power is +4 dBm to 22 GHz and 0 dBm to 26 GHz.

Failure rates are of major concern to users of modern sophisticated instruments. The excellent reliability of the 8672A has not been compromised in the design of the 8673A. A number of service features and diagnostics have been incorporated to reduce repair time.

#### **System Operation**

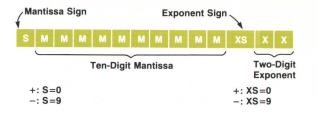

The organization of the 8673A is similar to that of the 8672A. The digital control unit (DCU), containing a mi-

**Fig. 1.** The HP 8673A Synthesized Signal Generator features metered AM, low-distortion FM, and high-performance pulse modulation. Its frequency range is 2 to 26.5. GHz.

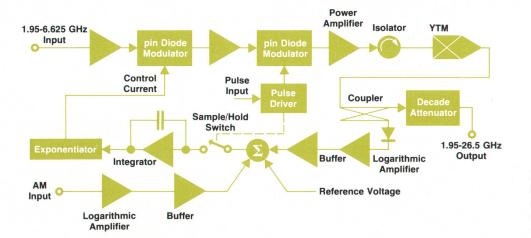

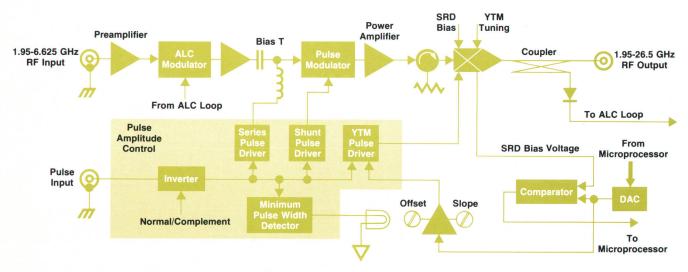

**Fig. 2.** Block diagram of the 8673A RF output section showing the major microwave components and the automatic level control (ALC) circuitry.

croprocessor, directs the internal oscillators, switches, attenuators and digital-to-analog converters (DACs) to appropriate operating points to produce the frequency, level, and modulations requested by the user either via the front panel or remotely via the HP-IB (IEEE 488). The frequency synthesis section is similar to that of the 8672A. This section includes a 2-to-6.625-GHz YIG-tuned \* oscillator (YTO) which is phase-locked to signals derived from a stable 10-MHz reference oscillator. The RF output section contains a YIG-tuned multiplier (YTM) which either passes the amplified YTO signal or multiplies it by 2, 3, or 4 to cover the 2-to-26.5-GHz frequency range (see article, page 10). A block diagram of the RF output section is shown in Fig. 2. The signal from the YTO is amplified and passed through a pin diode modulator for amplitude modulation and level control (ALC). Pulse modulation is performed in the subsequent series/shunt diode modulator before power amplification and multiplication in the YTM.

A number of benefits accrue from this configuration, in which pulse modulation is performed ahead of the multiplier. Adding a modulator after the YTM would absorb valuable power, particularly at the higher frequencies. The design of such a component to 26 GHz would be difficult, especially if the desired pulse on/off ratio of 80 dB is to be maintained. Another advantage of modulation ahead of the multiplier is the virtual elimination of pulse video feedthrough by the filtering action of the YIG filter in the YTM. A disadvantage of this system is the deterioration of pulse rise time through the YTM. The approach used in solving this problem is discussed in the article on page 10.

The multiplier is driven by a broadband GaAs FET power amplifier which produces a typical output power in excess of +27 dBm.<sup>4</sup> After multiplication in the YTM, the signal passes through a broadband directional coupler that has a leveling detector at the coupled port. The detected dc voltage is fed through a logarithmic amplifier and summed into the ALC loop. In pulse mode, the ALC loop error signal is generated by sampling during the on time of the pulse and holding between pulses. To achieve accurate leveling of pulses down to 100-ns pulse widths, the sampling gate window must include only the flat top of the sampled pulse, yet be as broad as possible to maximize effective duty cycle.

\*The frequency-determining element is a sphere of yttrium-iron-garnet in a magnetic field. Its resonant frequency is tuned by varying the magnetic field strength. Thus the rise time of the detected pulse must not be degraded through the detector and logarithmic amplifier. This requires a low bypass capacitance (3 pF) for the detector and sufficient bandwidth for the logarithmic amplifier. The actual gain-bandwidth product exceeds 500 MHz.

After the leveling coupler, the signal passes through a step attenuator which provides a maximum of 90 dB of attenuation in 10-dB steps. Continuous control of power levels between steps is provided by the ALC loop reference voltage which is adjustable by means of the vernier knob on the front panel. In remote operation, a DAC provides the reference voltage in 0.1-dB steps.

#### Performance

The instrument performance specifications are published only after characterization of a sufficient number of instruments to provide meaningful statistical data. The specification allows for measurement uncertainties (usually calculated to achieve 95% confidence levels), temperature and environmental variations, and any potential drift that may occur over time. For these reasons, measured room-temperature performance may be better than a specification might indicate.

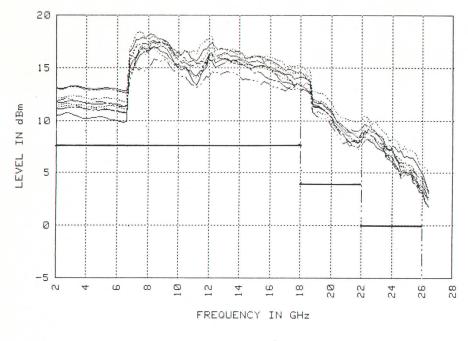

Maximum power output of a signal generator is of major concern to users interested in using the instrument as a local oscillator or where measurement system losses are high. Fig. 3 is a plot of maximum output power obtained from ten production 8673A instruments together with specified power as a function of frequency. The graph shows the margin between the specifications and the power available at room temperature.

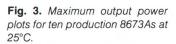

The level accuracy of the instrument is important to those measuring receiver sensitivities or the transmission characteristics of amplifiers or other devices. Fig. 4 shows level accuracy plots for ten production instruments for several ranges down to -100 dBm. In view of the excellent results obtained, it was decided that microprocessor correction of output level was not needed, eliminating the disadvantages of requiring new ROMs when components after the YTM are replaced.

Fig. 5 shows typical pulse performance at 26 GHz. Specified maximum rise time is 35 ns and maximum overshoot is 20%. Leveling accuracy down to 100-ns pulse widths is  $\pm 1$  dB relative to CW. To achieve 80-dB on/off

MAXIMUM POWER OUT

ratio, careful shielding of components is required. Leakage or radiation from components ahead of the pulse modulator is kept low enough not to leak back and be amplified by the power amplifier's 25 dB of small-signal gain.

#### Programmability

The 8673A is fully programmable via the HP-IB from an external controller. Extensive design effort went into making the remote programming as user-friendly as possible.

One HP-IB innovation is the master-slave sweep. This is

useful in testing of receivers and mixers where it is necessary to have two signal generators sweeping with a fixed offset between their output frequencies. One 8673A is designated as the master unit and sends out HP-IB commands to one or more slave 8673As. Master-slave sweep can be performed without a computer to control the system. The slave holds off the HP-IB handshake until its output has settled. The master looks for release of the handshake before proceeding to the next frequency. This ensures that the two synthesizers track each other.

**Fig. 4.** Level accuracy range for ten production 8673As at 0 dBm, -70 dBm, and -100 dBm output levels.

**Fig. 5.** A typical 8673A RF pulse at a carrier frequency of 26 GHz. The horizontal scale is 20 ns/div.

Of particular interest to system programmers trying to achieve maximum performance is the ready bit in the HP-IB status byte. The 8673A may take different times to settle after a frequency change. By sensing when the 8673A has actually settled instead of always waiting for a fixed worstcase delay time, the test system can run faster. The ready bit indicates that the 8673A has phase-locked and finished the YTM autopeak routine (see page 12) at a new frequency. The ready bit can be configured by a user program to generate a service request interrupt. Using this feature, the computer can be performing other useful work while the 8673A is busy.

Rear-panel output connectors provide sweep and blanking voltages for sweep displays on recorders, oscilloscopes, or network analyzers such as the HP 8755C or the HP 8410B/C. Stop-sweep and trigger outputs required for operation with network analyzers are available from a 14-pin connector on the rear panel of the 8673A.

Other interfaces provided at this connector permit useful functions without the need for an HP-IB controller. These include remote frequency incrementing and decrementing, a trigger-sweep input, an end-sweep output, blanking of the frequency display, and sequential storage register recall.

#### **Digital Control Unit**

One of the design objectives of the 8673A was to replace the combinational logic control section of the 8672A with a microprocessor. By using circuit boards and software designed for the 8662A 0.01-to-1280-MHz Signal Generator, it was possible to make a first breadboard controller capable of keyboard entry of microwave frequencies in a matter of weeks. With a base of proven circuits as a starting point, the development effort concentrated on user friendliness and enhanced performance of the analog circuitry and serviceability to try to match the expected applications.

One of the features of the 8673A is digital sweep. The digital control unit (DCU) can completely synthesize a sweep from a series of discrete frequencies. The sweep range can be entered as either start-stop or center frequency- $\Delta f$  (span sweep). The DCU has the necessary firmware to calculate either pair of values from the other. For example, if the user enters a start frequency of 10 GHz and a stop frequency of 5 GHz, the 8673A will calculate a center frequency of 7.5 GHz and a  $\Delta f$  of -5 GHz.

One area in which the 8673A departs from conventional analog sweepers is in the control of sweep rate. The 8673A is primarily a microwave synthesizer, so sweeps must be divided into discrete steps. The user can enter the number of steps or the step size. Obviously, the more steps to be generated, the slower a sweep will be. The other aspect of sweep rate is the time per step. In a synthesized signal generator, this time is the sum of the transition time between frequencies and the dwell time on each frequency. The 8673A can achieve a faster overall sweep rate by allowing the user to specify the dwell time. The DCU automatically checks the loops for phase lock after each step and controls the timing and Z-axis blanking accordingly.

For automatic sweep with dwell times shorter than 5 milliseconds, the DCU does not wait for a complete phaselock of all four loops. A heuristic algorithm considers which phase-locked loops are required to change on a particular step and estimates the required delay to be "close enough" that the frequency error will not be significant on most swept displays. As a result, the overall sweep time can be reduced. This makes the 8673A useful for such applications as aligning a circuit while watching a real-time swept display. At the same time, the synthesized nature of the 8673A eliminates the effects of drift commonly associated with analog sweepers on narrow sweeps. If the application requires a complete phase lock at each step, the user can simply enter a dwell time of at least 5 ms and the 8673A will give a complete phase lock.

The microprocessor-based controller of the 8673A is used in several ways to improve performance over that of the earlier 8672A. The most striking of these is the autopeak function. The microprocessor adjusts the tuning of the YIG-tuned multiplier to track the output frequency for maximum power and best modulation performance. This is described in detail in the box on page 12.

A number of internal features add measurably to overall ease of use and performance. For example, the 8673A has a number of functions that need timing. Instead of programming the microprocessor to go into a delay loop counting down numbers until the necessary time has elapsed, which would restrict the 8673A to performing one function at a time, an LSI multiple-timer IC and the basics of real-time, multitasking programming are built in. This allows the 8673A to do several things simultaneously.

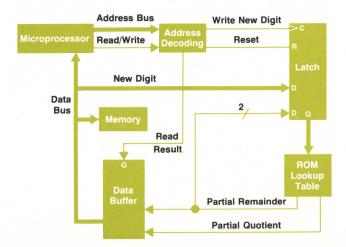

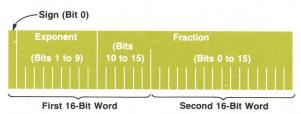

Another internal feature is the hardware divider circuit. Whenever the 8673A output frequency is above 6.6 GHz, the frequency of the YIG-tuned oscillator must be multiplied. From the perspective of the DCU, the desired frequency must be divided to calculate the YTO frequency. For output frequencies from 6.6 to 12.3 GHz, the YIG-tuned multiplier multiplies by 2, so the DCU needs to divide by 2. Division by 2 is fairly easy. The binary number is simply shifted one place to the right. For output frequencies above 18.6 GHz, the YTM multiplies by 4, so the DCU must divide by 4. Division by 4 can be done by two divisions by 2. However, from 12.3 to 18.6 GHz, the YTM multiplies by 3

# Sample-and-Hold Leveling System

### by Ronald K. Larson

Design goals for the 8673A's automatic level control (ALC) system were as follows:

- Broadband power leveling from 2.0-26.5 GHz in pulse, CW, AM, and FM modes

- Good AM performance (10 Hz to 200 kHz, 0 to 90% depth) with a stable leveling loop

- Temperature-stable output power from -10 to +10 dBm

- External leveling capability using a power meter or a diode detector

- Pulse duty cycle as low as 0.0001

- Minimum power transients when changing frequency or power

Full HP-IB control.

- The leveling loop is shown in Fig. 2 on page 4.

One of the most difficult problems to solve in a very broadband leveling system is caused by the variation in gain with frequency of the components in the microwave signal path. In a conventional or linear leveling loop the voltage-gain variations directly produce loop-gain variations. This can cause loop stability problems and degrade AM performance. Also, it is usually desirable for a microwave signal generator to control and meter output power in dBm rather than volts. With a linear loop, the system reference voltage must be a nonlinear function of power out in dBm, and therefore cannot be used directly to control a meter calibrated in these units.

The use of a logarithmic amplifier in the feedback path of the loop has a valuable effect—the microwave gain of each part of the signal path in the leveling loop does not affect loop gain. Instead, the gain factor for each microwave component operating linearly is 1 dB/dB. The YTM is a nonlinear voltage-gain device but exhibits a nearly constant gain in dB/dB, when properly biased, for each multiplying band and over the full range of power output. Typical gain factors for the YTM are 1.0, 1.4, 1.6, and 1.8 dB/dB on bands 1, 2, 3, and 4, respectively. A factory-set loop-gain adjustment in the leveling system for each multiplying band compensates for the YTM gain changes.

A detector operating in its square-law region will produce a large voltage-gain variation as power output varies. This would produce another source of loop-gain variation in a linear loop. In the logarithmic loop the gain factor is simply 2 dB/dB, greatly reducing loop-gain variations.

Thus the log amplifier reduces total loop-gain variations to a few dB over the entire range of power and frequency. Loop gain is also independent of variations in small-signal gain that can occur in the microwave amplifiers. The result is a loop with nearly constant AM bandwidth and excellent stability.

When the log amplifier is used, its voltage output varies linearly with power output in dB. Thus the reference voltage into the summing junction is linear with RF power out in dBm. This simplifies the control and metering of output power since the reference voltage need not be shaped and can be used directly to control the deflection of a meter calibrated in linear dBm units.

The exponentiator following the integrator lets the integrator voltage control the modulator output power linearly in dB. The exponentiator gain factor is 0.9 decade of current per volt input. The pin diode modulator has the property that any decade of input current produces the same dB change in output power. The exponentiator/modulator cascade has a sensitivity of 36 dB/volt at the integrator output.

To produce amplitude modulation in the loop, the modulation voltage is summed into the summing junction after being logarithmically shaped. Shaping is necessary to produce RF envelope voltage variations that are linear with the AM input voltage. The resultant AM typically has less than 5% distortion at 90% depth and 100 kHz rates. YTM linearity in dB/dB is a definite factor in achieving this kind of AM performance. The YTM using self-bias rather than fixed bias can maintain bias stability, freedom from parametric phenomena, and a nearly constant gain factor over its full dynamic range. The actual dynamic range needed for power output from -10 to +10 dBm in CW mode with 90% AM depth is 40 dB. Microwave amplifier compression can add another 10 to 15 dB. Therefore, the total ALC loop dynamic range is 50 to 55 dB.

The voltage output of the detector varies with temperature. The temperature coefficient (TC) varies with power level. To correct for this varying TC, the logging amplifier has a thermistor in a resistor network to correct for detector drift at -4 dBm power output. This leaves a residual drift term at all other power levels which must be corrected. This term is proportional to power level in dB. It is corrected by using a linear-TC resistor in the reference voltage circuit. The result is typically less than 0.1 dB of drift over the specified temperature range of 15 to 35°C and over the full range of power and frequency.

Operation of the leveling loop in the pulse mode is identical to the CW mode since the sampling switch is closed only when RF is on. When the switch is open the integrator capacitor holds its charge, thus maintaining constant output voltage. The current into the pin modulator is constant when the RF is off. When RF again turns on, the switch closes and any charge that may have leaked off the capacitor is replaced. This design—where the loop actually samples the error voltage—eliminates the requirement seen in some peak-leveling systems to slew the hold capacitor voltage to the full value of the pulse on each RF pulse. The integrator capacitor also provides the system's dominant pole.

The ALC loop has two selectable bandwidths. The wide bandwidth allows high rates of amplitude modulation on a carrier and fast transient response. The narrow bandwidth is used for CW signals and reduces AM noise on the carrier, but has slow transient response. The 8673A's digital control unit automatically selects the wide bandwidth whenever the frequency is switched and then switches to the narrower bandwidth when appropriate. This allows the ALC circuit to recover more rapidly after a frequency change. Switching the ALC bandwidth as a function of frequency switching, modulation, and sweep mode would be impractical without a microprocessor. and so the DCU must divide by 3. A general-purpose division routine for the microprocessor would take more than 20 milliseconds for this division. This is more than the specified worst-case frequency switching time! It would be unacceptable to require that much DCU processing time for certain output frequencies.

The design used for division by 3 in the 8673A includes a special circuit, Fig. 6, to speed up this process. The microprocessor starts the division cycle by clearing the latch of any possible remainder from a previous calculation. Then it gets the first digit of the frequency from memory and writes it to the latch. For example, for a frequency of 12,345,678 kHz, this is a 1. the latch stores the 1, and in turn drives the ROM with 01. On the next instruction, the microprocessor reads the ROM output through the data buffer. In our example, it will read a partial quotient of 0 and a remainder of 1. When the microprocessor writes the next digit (2 in the example) to the latch, the remainder from the previous digit is automatically put into the latch at the same time. A dividend of 2 and a remainder of 1 from the previous digit combine to make 12. This will divide by 3 to give 4 with 0 remainder. By freeing the microprocessor from manipulating the remainder between digits and from calculating the absolute table address for each digit, the division routine for an eight-digit number can be accomplished in less than 0.2 millisecond. This is 100 times faster than the generalpurpose software routine, and almost as fast as division by 2.

#### **Electromagnetic Compatibility**

One of the classical problems in digital system design is that digital circuits tend to generate electromagnetic interference. Preventing the signals generated in the 8673A's digital control unit from coupling to other circuits required several measures. The first and primary measure was to design the hardware and firmware so that the microprocessor spends most of the time in a wait-for-interrupt state. When this happens, almost all of the logic lines in the DCU are quiet. As a second precaution, the buses carrying control signals to the front panel, phase-locked loops, and output section are all driven by latches. The latch outputs only change when necessary. This further confines the gen-

**Fig. 6.** This circuit reduces the time it takes to divide by 3 by a factor of five over a software method.

eration of noise to the DCU. These precautions plus good engineering practice with grounds and bypass capacitors reduce the coupling and radiation of digitally generated signals to a level well below the specified limits. The 8673A passed the radiated-electromagnetic-interference test the first time a prototype was put in the screen room. Just the same, extensive type testing was performed to verify that nothing had been overlooked.

#### Reliability

With the increasing complexity of today's instruments reliability becomes a major concern. Considerable effort was devoted to thermal design, component ratings, vendor history and stress analysis during the design of the 8673A.

Statistics acquired over the last five years since the introduction of the 8672A indicate a warranty failure rate well below the original goal. Actual warranty rate is about 32% per year, or an MTBF of 6700 hours assuming an operating time of 2000 hours per year for the instrument's 3100 components.

The 8673A design followed the successful approach of the 8672A. Thermal profiles of the instrument were done to measure local temperature rises and to check that average rise was less than 10°C above ambient. The increased power dissipation of the 8673A led to a more massive heat sink and supplemental individual heat sinks for the series-pass power supply transistors. A stress analysis computer program was used to evaluate each component in its operating environment to verify that internally generated derating guidelines were not exceeded. Careful failure analyses were performed on failed components to gain an understanding of the failure mechanisms and to provide vendors with appropriate information to rectify the problem. The failure rate analysis program, from which the 8672A failure rate has been accurately computed, predicts an 8673A MTBF greater than 5400 hours for 3320 components.

#### Serviceability

A number of features allow fast and easy troubleshooting if a failure does occur. First, every time the power is turned on, the DCU does a self-check of RAM and ROM. If a failure is detected, a code indicating the suspect IC is displayed on the front panel. During operation, if the DCU detects an abnormal condition, it displays a message on the front panel. For example, an output power unleveled condition causes the ALC UNLEVELED annunciator to be lit. This could be an indication of a malfunction, or simply that the user is trying to get more than the specified power at that particular frequency. Less likely failures are indicated by message numbers that are explained on the pull-out card. The DCU always attempts to continue operation. Despite a problem, the 8673A may still be useful for the particular measurement and service can be scheduled for a more convenient time.

A special function key accessible when the top cover is open (or via the rear-panel programming connectors) makes it possible to use the controller section to simplify servicing the other portions of the instrument. For example, in the 8672A it is necessary to connect a low-frequency function generator to the YTM drive circuit as part of the procedure to measure the passband and align the circuit. The 8673A can simply sweep the YTM fine-tuning DAC to generate the ramp. The push of a couple of buttons eliminates the need for a piece of test equipment.

The HP 11726A Service Support Kit includes some special active extender boards. The primary purpose of these boards is to allow the service technician to tell quickly whether a problem is in the controller or elsewhere. For example, if the front-panel frequency entry and display appear to function but the output frequency is wrong, the problem could be in the controller or in a phase-locked loop. The numeric display on the extender board shows the DCU frequency output in decimal numbers. This makes it quick and easy to verify that the DCU is functioning properly.

If the digital circuitry is malfunctioning, a number of tests facilitate component-level troubleshooting. A key part of these tests is a 2K-byte ROM which is used only for troubleshooting purposes. Normally, its data outputs are not connected to the rest of the controller circuitry. The debug ROM contains a test program that tests not only the other ROMs but also itself. If the debug ROM does not pass the test, the next step is to put the microprocessor into a freerun mode and use signature analysis to verify the address decoders and the debug ROM data. If this doesn't find the problem, it is time to check the clock waveforms and the power supply voltages.

A dozen other routines are included in the debug ROM. Each routine is designed to test a specific part of the 8673A. Many of these tests also use signature analysis. For example, one routine exercises all of the digital logic in the output section. Each of the control latches is cycled through all valid data settings and each of the three DACs is stepped through a voltage ramp. If the DAC output waveform is not a simple staircase ramp, digital signatures can be taken at the DAC input with the same test setup.

#### Acknowledgments

The capable design team responsible for the 8673A had many contributors besides the authors in this issue. Credit goes to Ron Kmetovicz for the original concept and for his leadership, to Charles Cook for the product design, and to John Hasen for the design of the YTM driver, the DAC circuitry, and the test system. Dave Veteran was responsible for the improved step attenuator design. Jerry Ainsworth and Derrick Kikuchi worked on the pulse circuitry. Randy White was the reliability engineer. Don Pierce was responsible for the microcircuit production engineering and John Sims and Ray Yetman were the instrument production engineers. Eric McHenry contributed to the test system software. Donn Mulder was the product marketing engineer.

#### William W. Heinz

Bill Heinz has been with HP for seventeen years. He's been a diode applications engineer, a designer of microwave components and oscillators, and a project manager for synthesized signal generators, the latest being the 8673A. A senior member of the IEEE, he has coauthored several published letters on ferrite devices and a paper on a microwave amplifier. His work has resulted in a patent on a microstrip resonator. Bill was born in Havana, Cuba and attended the Polytechnic Institute of Brooklyn, receiving his BSEE degree in 1960 and his MSEE in 1962. Before

coming to HP he worked with masers, paramps, cryogenic ferrite components, and superconducting magnets for five years. He lives in Palo Alto, California, has two sons, and likes to travel abroad, hike, listen to music, and attend the theater.

#### Paul A. Zander

Paul Zander participated in a co-op study program with General Motors Institute in Flint, Michigan and received the MS degree from Purdue University before joining HP in 1970. He has been responsible for a number of analog and digital design tasks, most recently the hardware and software for the digital control unit in the 8673A Synthesized Signal Generator. Two patent applications have resulted from his work on the 8673A. A native of Cleveland, Ohio, and a member of the IEEE, Paul is married, has two children, and lives in Los Altos, California. He is building a home com-

puter, enjoys photography and running, holds the amateur radio call sign AA6PZ, and has had several magazine articles published about his station.

#### References

1. J.L. Thomason, "Expanding Synthesized Signal Generation to the Microwave Range," Hewlett-Packard Journal, Vol. 29, no. 3, November 1977.

2. K.L. Astrof, "Frequency Synthesis in a Microwave Signal Generator," Hewlett-Packard Journal, Vol. 29, no. 3, November 1977.

3. B.C. Stribling, "Signal Generator Features for a Microwave Synthesizer," Hewlett-Packard Journal, Vol. 29, no. 3, November 1977.

4. M. Furukawa, "A Broadband 2-to-7-GHz Power Amplifier," Hewlett-Packard Journal, Vol. 33, no. 2, February 1982, p. 20.

# A Wideband YIG-Tuned Multiplier and Pulsed Signal Generation System

by Ronald K. Larson and Lawrence A. Stark

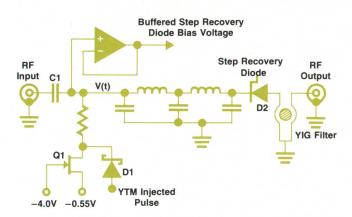

HE KEY TO THE 2.0-to-26.5-GHz frequency range available at the output of the 8673A Synthesized Signal Generator (see article on page 3) is a broadband YIG-tuned multiplier (YTM), which is shown schematically in Fig. 1. YIG stands for yttrium-iron-garnet, a ferrite material. When a YIG sphere is placed in a magnetic field, it exhibits a sharp resonance at a frequency that is a function of the magnetic field strength.

The operating frequency range of the YTM is divided into four bands, which correspond to frequency multiplication ratios of 1, 2, 3, and 4. In band 1, step recovery diode D2 in Fig. 1 is forward-biased to a low impedance and no significant harmonic generation occurs. The four bands and the corresponding frequency ranges are listed below.

| Band<br>Number | Output Frequency<br>Range (GHz) | Input Frequency<br>Range (GHz) |

|----------------|---------------------------------|--------------------------------|

| 1              | 2.0 - 6.6                       | 2.0 - 6.6                      |

| 2              | 6.6 - 12.3                      | 3.3 - 6.15                     |

| 3              | 12.3 - 18.6                     | 4.1 - 6.2                      |

| 4              | 18.6 - 26.5                     | 4.65 - 6.625                   |

The YTM consists of a standard step recovery diode multiplier which generates a comb of harmonics of the input frequency. The input frequency is tunable over a broad range and the multiplication ratio is varied by tuning a YIG filter to select a single harmonic component. The multiplier is inherently broadband in that the comb spectrum generated by the diode extends from the input frequency to an upper limit greater than 30 GHz. By tuning the YIG filter at

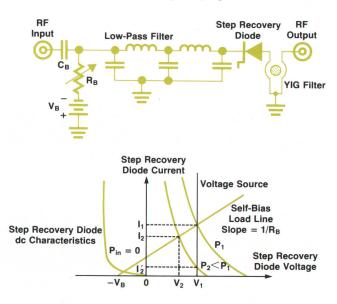

**Fig. 1.** YIG-tuned multiplier schematic. At output power levels greater than approximately 0 dBm, the steady-state value of the step recovery diode bias voltage V(t) is directly proportional to the RF input voltage. The FET resistance is controlled to give the highest conversion efficiency consistent with stable parametric-free RF output.

the output of the multiplier to one particular harmonic, all unwanted output signals are suppressed and the desired frequency is delivered to the output of the device. The input low-pass filter prevents the output signals from returning to the input and prevents harmonics of the power amplifier feeding the YTM from interfering with the multiplied signal.

In the multiplying bands, the step recovery diode is biased to act as a charge controlled switch which produces a narrow voltage impulse when the diode switches from forward to reverse bias. The impulse width is determined by the circuit inductance and the diode capacitance, assuming that the transition time of the diode is negligible. Impulse widths of 40 picoseconds are necessary to obtain high conversion efficiency at 26 GHz, and since the diode transition time should be a small fraction of the pulse width, it is very important to obtain diodes with low capacitance and short transition times.

The proper timing of the switching action is controlled by the dc self-bias voltage. The ideal timing point for switching to low capacitance occurs when the diode current has reached its maximum value. The resulting diode voltage impulse goes negative initially and then positive, at which point the diode switches back to the conducting state.

The input loop inductance of the YIG filter and the diode capacitance form the resonant circuit for the impulse generator. The input low-pass filter provides an impedance match at the input frequency and a short circuit to harmonics.

#### **Mechanical Design**

The complete multiplier is constructed on a single sapphire substrate. The design goal is to provide the closest possible physical proximity between the step recovery diode and the YIG output filter. This increases the broadband capabilities of the circuit by reducing the path length of the unwanted harmonics that are reflected from the YIG filter back to the diode.

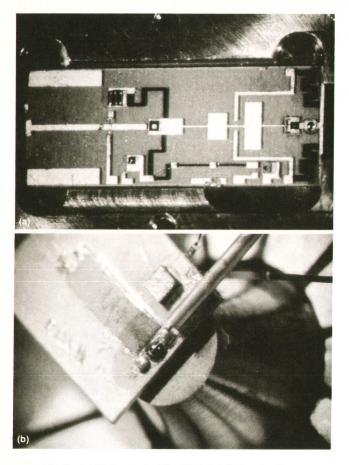

Fig. 2 shows a photograph of the region around the YIG filter and step recovery diode. The diode is die-attached to the top surface of the chip capacitor which is the final element of the input low-pass filter. The capacitor is epoxied to the heat sink, which provides an extension of the ground plane in the region of the rectangular hole. This opening is laser-cut, while the circular hole that holds the 0.023-inch-diameter YIG sphere is drilled ultrasonically.

The assembled substrate is held in a magnetic package consisting of a center body and two magnets. The design of this package provides differential expansion of the magnets and the center body so that the gap between the magnet pole faces remains constant when the temperature of the struc-

**Fig. 2.** (a) Photograph of the YTM circuit showing the components and filter. (b) Photograph of the microcircuit showing the ground plane, YIG sphere, and output coupling loop.

ture changes. This keeps the YIG filter tuned precisely to the output frequency.

#### Input Low-Pass Filter

Optimizing the input low-pass filter for a resonance-free stopband up to 26.5 GHz was a major effort. The transverse resonances in the distributed transmission line filter elements forced a modification of the basic design, which was derived from standard filter element values. It was evident that the final capacitive element in the low-pass filter could not be realized on the 0.01-inch-thick sapphire substrate. A thinner dielectric was needed to push the transverse resonances past the upper frequency limit of 26.5 GHz. A 0.004inch-thick single-dielectric capacitor with a nominal value of 2.0 pF was chosen empirically on the basis of performance in actual circuit tests. This was significantly lower than the prototype value of 2.7 pF.

#### **Step Recovery Diode Characteristics**

Two different step recovery diodes (SRD) have been used successfully in these YTMs. Both were developed for inhouse use at Hewlett-Packard. One diode is an outgrowth of HP's standard SRD product line and the other was developed by HP's Santa Rosa Technology Center as a second source. A major effort in the development of this device was to keep the doping profiles as abrupt as possible. Coupled with intrinsic-layer thicknesses less than 1  $\mu$ m, this was seen as the key to obtaining the shortest possible transition time. Two other diode parameters of importance are the reverse bias capacitance and the recombination time. As the diodes are made physically smaller, the recombination time begins to drop because of the influence of the sides and contacts of the device. Many different diodes were evaluated to select the optimum junction capacitance for maximizing the conversion efficiency at 26 GHz. The final diode dimensions are a compromise among aspect ratio, capacitance, breakdown voltage, and transition time.

#### **Bias Control**

Optimum RF multiplication requires that the appropriate dc conditions be established for the diode. This is done through a separate bias circuit. A blocking capacitor prevents the dc from flowing in the microwave input circuit. Fig. 3 shows how the SRD's dc operating point is dependent on the microwave signal amplitude. The circuit that supplies these dc conditions is called a self-bias circuit because the dc operating point is established by the microwave signal input amplitude. The advantage of the selfbias circuit is that a stable operating point is obtained easily over the full dynamic range of the multiplier because the dc conditions follow the RF power level smoothly. The correct operating point is determined by the bias resistance. If the bias resistance is set lower than the optimum value, the multiplication will be stable, but the power output will be low. As the bias resistance is raised, an optimum point is found where the power is high and the operation is still stable. At higher resistance, either the output power drops, or the operation becomes unstable.

It has been found empirically that the optimum self-bias resistance is a function of frequency within a single multiplying band. To provide for this variation, a single JFET chip is used as a voltage-controlled resistor on the multiplier substrate. The resistance is controlled by adjusting the gate voltage.

Another way of establishing the proper dc bias is with a

Fig. 3. Self-bias circuit operation.

# Autopeaking

# by Paul A. Zander

One aspect of the YTM's performance is that it acts as a very narrow bandpass filter that tracks the source output frequency. If the tuning is off by as little as 10 MHz, maximum available power is reduced, the pulse modulation waveform is distorted, and the frequency modulation sidebands are filtered asymmetrically.

Avoiding these problems requires tuning accuracy better than 0.1%. Because of nonlinearities, hysteresis, and temperature sensitivities in the YTM, this kind of tuning accuracy is impractical to achieve in a straightforward open-loop tuning system. Autopeak is a combination of a small amount of hardware and 1500 bytes of microprocessor code that adjust the YTM tuning to the exact center of the passband (see Fig. 4 on page 13).

Because the peaking process introduces some perturbations on the output which could affect certain measurements, peaking is never allowed to occur spontaneously. Peaking can be prevented by a front-panel pushbutton or an HP-IB command.

Peaking is performed in conjunction with a number of operator inputs. It occurs whenever peaking is switched on, when the RF output is switched on or the FM deviation range is changed, and after every frequency change that results in an output frequency more than 50 MHz away from the last one where peaking was performed. Because peaking is critical to achieving good pulse performance, peaking is automatically enabled and performed each time the pulse modulation function is turned on. The time required for peaking depends on the YTM passband shape and the amount of correction required. To maximize the measurement rate in automatic systems, a bit in the HP-IB status byte is set to indicate that peaking has been completed. This can be used by the HP-IB system as an interrupt to initiate the next part of an measurement cycle, thus preventing the taking of false data during the peaking routine.

#### The Peaking Algorithm

The peaking process consists of four phases: setup, tuning the YTM, measuring the YTM self-bias (for pulse injection), and restoring normal operation of the 8673A. During the setup phase, the digital control unit (DCU) suspends normal operation of the output section. All modulation is switched off. The internal diode ALC detector is selected. If a very large frequency step has just occurred, some delay is used to allow the YTM frequency to settle completely before using the peaking as a fine tuning adjustment. Then the ALC circuit is put into hold mode using circuits already included for the sample-and-hold operation during pulse modulation. Control flags are set in software so that the 8673A can accept front-panel and remote commands to turn on modulation, but not execute the commands until peaking has been completed.

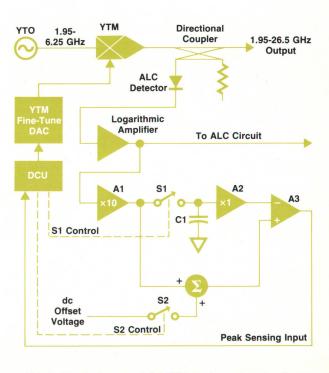

In the peaking process, the DCU uses an eight-bit digital-toanalog converter to tune the YTM  $\pm$ 200 MHz in steps of 1.6 MHz. The peak sensing circuit, Fig. 1, is used by the DCU to direct the search for the center of the passband. Buffer amplifier A1 amplifies the output of the detector logarithmic amplifier in the ALC circuit. Because of the ALC log amp, a change in the YTM output of 1 dB causes a change of 300 mV at the output of A1 regardless of the absolute power. A2, C1, and S1 act as a sample-and-hold circuit which is controlled by the DCU. A3 compares the output of the sample-and-hold circuit, which represents a previous YTM tuning setting, with the present output of A1 and sends the result to the DCU. The entire circuit consists of a quad FET operational amplifier IC and a few discrete parts. An offset corresponding to 3 dB can be switched in before A3. Without the offset, the output of A3 will change when the present YTM output is less than when the sample was taken. With the offset, the comparator output will not change until the YTM output is 3 dB less than the sample. The timing of the sample-and-hold operation, and whether the offset is on or off, depends upon which of two algorithms the DCU is using.

In the coarse tuning algorithm, the offset is not used. The DCU closes S1 long enough to charge C1 and then opens S1. Thus a voltage proportional to the RF power is held on C1. Next the YTM is tuned 10 MHz. After a delay of 200 microseconds to allow the tuning coil time to respond, the DCU checks the output of A3. If the microwave output power is greater at the new tuning setting, the output of A3 will be high, otherwise it will be low. If the power is higher, the DCU repeats this process of sampling the output power on C1, tuning the YTM to a new setting and checking to see if the YTM output is greater or less. With suitable refinements to ignore minor resonances in the YTM passband shape, this algorithm does a good job of locating the main peak of the passband. However, it does not do a repeatable job of finding the exact peak. Instead, it tends to stop at a point a fraction of one dB past the true center of the YTM passband. For achieving maximum power output, it is adequate and represents a major improvement over the older HP 8672A, which has no automatic peaking. However, the pulse and frequency modulated signals show some distortion with even a small amount of mistuning, so a second algorithm is built into the DCU.

Fig. 1. Block diagram of the YTM peak sensing circuit.

The basic problem with the coarse tuning algorithm is that the power output changes very slowly as the YTM tunes through the middle of the passband. Finding the exact middle becomes an example of the classical measurement problem of accurately finding the small difference between two large values. The solution was to develop a centering algorithm.

The centering algorithm is based on the fact that the YTM passband shape is reasonably symmetrical in the region from 3 to 15 dB below the peak. The DCU performs the centering algorithm by first assuming that the initial tuning point is close to the peak. It samples and holds a voltage on C1 which corresponds to the initial power output. Then it switches in the offset voltage corresponding to 3 dB and starts stepping the YTM until the comparator output changes. This point corresponds to an output power level 3 dB less than the original point. Next the DCU returns to the original point and starts stepping the YTM tuning in the other direction until the other 3-dB point has been located. The center of the passband is calculated to be halfway between the 3-dB points. Because the YTM passband is symmetrical, it makes no difference whether the original point was at the exact center or slightly below the center.

Normally, the open-loop tuning is accurate enough that the centering algorithm alone is adequate. For small frequency steps, the time to search is further reduced by starting at the tuning correction for the previous frequency. Only when the centering algorithm encounters a difficulty, such as when the YTM tuning has been grossly pulled by a reactive load impedance, is the

voltage source. This works well at constant power, but requires external adjustment if the power level is varied. As shown in Fig. 3, as the power level drops, the operating voltage should drop too, so a voltage-source bias network needs to be adjusted as the input power to the multiplier is changed.

At low power levels there is not enough diode current to produce the required bias. The fixed bias voltage shown in Fig. 3 provides the needed bias on the knee of the SRD's dc characteristic.

#### **YIG Filter**

The YIG filter is central to the operation of the overall YTM. The operating characteristics that had to be dealt with were bandwidth, crossing modes, magnet alignment, outof-band rejection, acoustic squegging, and loop inductance.

The shape of the coupling wires affects nearly all of these

coarse tuning algorithm used.

#### **Bias Sample**

Once the YTM frequency has been tuned, the self-bias must be measured for use with pulse injection. This is only done in pulse mode. The DAC output that controls the pulse injection is compared with the actual YTM bias voltage for CW output at that particular microwave frequency. The DCU performs a straightforward successive approximation algorithm to measure the bias voltage. For a fixed frequency and output power level, that would be the end of it. However, the injection must change as the output power level is changed. If only the power is changed, the DCU skips the YTM tuning procedures and simply measures the bias for the new power level. The DCU eventually builds up a table in memory of bias versus power level every 0.4 dB at that frequency. Once the needed data is in the table, the DCU simply looks it up, thereby avoiding the possible user inconvenience of having the DCU continuously switching to CW so that the bias injection can be measured. Of course, when the YTM tuning is changed (for example, when the frequency is changed) the table of bias values is erased, and the data must be remeasured.

After the YTM tuning has been corrected and the bias measured, the DCU restores normal modulation and operation to the output section. The time it takes to perform this process varies somewhat with the amount of tuning needed, but is typically 5 to 10 milliseconds. In return for this brief delay, the 8673A delivers more output power and better modulation.

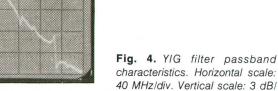

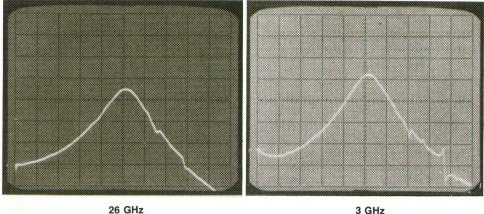

factors. The design uses tight coupling to maximize bandwidth and minimize loop inductance for narrow pulses. This leads to more severe crossing modes which have been minimized experimentally by optimizing the sphere orientation. As Fig. 4 shows, the YIG filter passbands are free of spurious modes and the 3-dB bandwidths are typically 60 MHz or more. A 3-dB bandwidth less than 40 MHz adversely affects the rise time of pulsed RF signals.

- The parameters of the YIG sphere are:

- Saturation magnetization  $4\pi M_S = 800$  gauss

- Diameter = 0.58 mm (23 mils)

- Operating temperature = 80°C

- Bias field axis =  $30^{\circ}$  off  $\langle 100 \rangle$  towards  $\langle 110 \rangle$

The YIG filter is temperature stabilized with a heater and thermistor feedback control which maintains the sphere at

div.

26 GHz

80°C, independent of external temperature changes.

Nearly all of the key specifications of the 8673A depend on whether the YIG filter is centered at the output frequency. An autopeak circuit (see page 12) controlled by the microprocessor ensures that the YIG filter is operating at the center of its passband. It works by making small corrections to the magnet current and monitoring the output of the ALC detector to find the maximum output power as a function of magnet tuning. Thus, output power is maximized and optimum pulse shape is maintained in the face of magnet tuning hysteresis and nonlinear tuning characteristics caused by reactive circuit pulling of the filter center frequency.

#### **Pulse Modulation System**

For the YTM to frequency-multiply microwave input pulses without producing excessively long rise times, the diode bias voltage V(t) must reach its steady-state value in a time at least as short as the rise time of the input microwave pulse. Using the self-bias scheme described earlier, the dc bias conditions are created by the rectification inherent in the operation of the diode. Because of charge storage in the step recovery diode, the rise time of the bias voltage V(t) is about 100 to 300 ns, producing microwave pulse rise times of approximately the same length.

The rise time of the output microwave pulse is longest at the high end of each multiplying band (e.g., at 12.3, 18.6, and 26.5 GHz). This occurs because reverse-recovery current of the SRD flows for a higher fraction of each input frequency cycle at the high end of each band. Hence it takes longer for the SRD bias voltage V(t) to reach its steady-state value and the output pulse rise time is correspondingly longer.

The method used to eliminate the rise time degradation of the YTM is to charge the capacitor C1 in Fig. 1 to the required final value before the arrival of the microwave pulse. In this way, V(t) is at the correct voltage when the pulse arrives, and the RF pulse passes through the YTM undistorted. C1 is charged by applying a short positive pulse to diode D1 before the RF pulse arrives. This pulse is called the YTM injected pulse. Using this technique, the microwave pulse rise time is limited only by the YIG filter bandwidth.

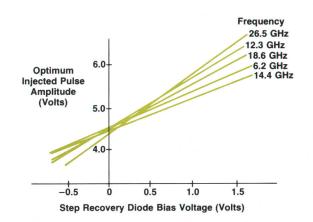

**Fig. 5.** The optimum injected pulse amplitude to eliminate rise time degradation is a linear function of the steady-state step recovery diode bias voltage.

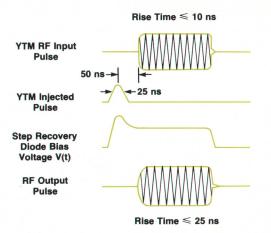

**Fig. 6.** Pulse injection forces the step recovery diode bias voltage to the correct value before the RF pulse arrives. Output rise time is then a function only of the YIG filter bandwidth.

The successful implementation of this system rests on the ability to predict the correct amplitude of the YTM injected pulse at each frequency and power level. Since the purpose of the injected pulse is to raise the bias voltage V(t) to the value it would have in normal operation, the first step is to measure the steady-state value of the diode voltage while the YTM is in CW operation. Then this voltage is used to control the YTM injected pulse amplitude.

One requirement for this system to work effectively is that the optimum injected pulse amplitude must be a linear function of steady-state SRD bias voltage. The proportionality factor and offset must be relatively constant over any multiplying band. A simple model of the circuit predicts and experimental data confirms that the required linear relationship exists and that the variation in slope and offset with frequency can be accommodated by adjusting the gain and offset of the circuit that controls the injected pulse amplitude. This adjustment is made by observing pulse shape on each multiplying band while adjusting the injected pulse amplitude.

Fig. 5 shows a graph of the optimum injection pulse amplitude as a function of the steady-state value of step recovery diode bias voltage V(t). Different values of bias voltage correspond to different microwave power levels at the input of the YTM. It can be seen that different slope and offset values are obtained depending on the operating frequency, although the total variation is not large. Within one multiplying band the variations are small enough that the behavior over the entire band can be adequately approximated by a single straight line.

Since the straight line is only an approximation, the actual RF pulse at a particular frequency can have either overshoot or lengthened rise time depending on whether the injected pulse amplitude is larger or smaller than the optimum value. The slope and offset parameters of the pulse control circuit that generated the curves in Fig. 5 are factory-set so that the total variation of rise time and overshoot is within the specified limits of 20% maximum overshoot and 35 ns maximum rise time. Typical performance is 10% maximum overshoot and 25 ns maximum rise time.

The pulse control system waveforms are shown in Fig. 6.

The timing of the application of the YTM injected pulse is critical and is fixed. The pulse arrives approximately 50 ns before the RF input pulse to allow ringing transients to die out of the SRD bias voltage V(t). When these transients die out, the SRD voltage is at the correct value and the output microwave pulse rise time is limited only by the bandwidth of the YIG filter.

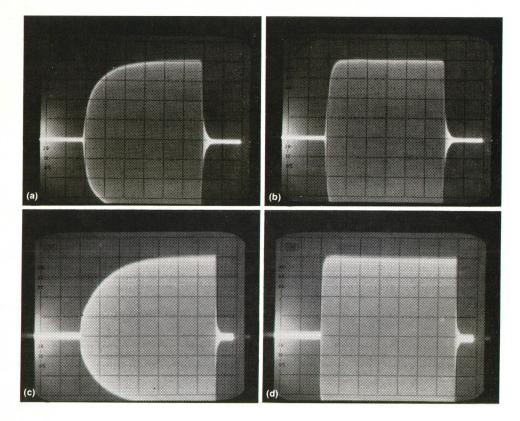

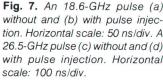

Fig. 7 shows pictures of RF pulse shapes that demonstrate the dramatic improvement in rise time as a result of the pulse injection.

The overall pulse modulation control system, Fig. 8, operates as follows. Whenever frequency changes by 50 MHz or more, or power changes by 0.4 dB or more, the input RF voltage to the YTM can change significantly. Thus the SRD bias voltage V(t) may change, which will change the required YTM injected pulse amplitude. To compensate for these changes the microprocessor switches the leveling system into the CW mode for about 200  $\mu$ s. During this time the microprocessor changes the DAC (digital-to-analog converter) output until it equals the steady-state value of bias voltage V(t). Pulse mode is then enabled and the injected pulse amplitude is again the correct value to produce short-rise-time pulses.

The DAC output voltage drives an amplifier, which provides a gain and an offset adjustment for each band. The amplifier output voltage controls the injected pulse

Fig. 8. 8673A pulse modulation system.

#### amplitude.

Another requirement in the reproduction of high-quality output pulses is that the RF pulse into the YTM must be free of ringing and overshoot. This is accomplished by using a series-shunt pulse modulator before the power amplifier.<sup>1</sup> This minimizes mismatch reflections between the preamp output and the power amplifier input. The series pulse driver provides a pulse to the series diode while the shunt pulse driver provides a pulse to the shunt pin diodes. This method achieves the low reflections of a series-shunt modulator and retains the short rise time of a shunt pin diode modulator.

Also included in the pulse modulation system is a pulse width detector which turns on the front-panel unleveled indicator when the input pulse width is less than 100 ns. The specified level accuracy at 100-ns pulse width is  $\pm 1$  dB relative to the CW level. Typically, specified level accuracy is maintained down to 80-ns pulse width. Pulse widths less than 80 ns are available but level accuracy is degraded. Maximum pulse repetition frequency for the specified level accuracy is maintained to 5 MHz, as shown in the table below.

#### **Pulse Performance Summary**

| Parameter                                       | Specified<br>Performance  | Typical<br>Performance |

|-------------------------------------------------|---------------------------|------------------------|

| Level Accuracy<br>(relative to CW)              | ±1.0 dB                   | +0.4 dB <sup>2</sup>   |

| Minimum Pulse Width<br>(for specified accuracy) | 100 ns                    | 80 ns                  |

| Minimum Duty Cycle<br>(for specified accuracy)  | 0.0001                    | 0.00003                |

| Maximum PRF<br>(for specified accuracy)         | 1 MHz                     | 5 MHz                  |

| Pulse On/Off Ratio                              | >80 dB                    | >90 dB                 |

| Overshoot                                       | 20%<br>(25%, 6.6-6.7 GHz) | 10%                    |

| Rise Time                                       | 35 ns                     | 20 ns <sup>1</sup>     |

1. Typical system performance gives rise time less than 25 ns on the multiplying bands and 15 ns on the 1.95-6.6 GHz band.

2. Typical level accuracy relative to CW is +0.4 dB at 100-ns pulse width.

#### Acknowledgments

We are grateful for the contributions of Don Pierce, Ray Yetman, John Sims, Bob Skinner, Sandy Smith, Pauline Prather, and Klaus Model. Thanks to Steve Sparks for his original development of the ALC loop.

#### Reference

1. R. Larson, "A Fast 2-to-8-GHz Pulse Modulator," Hewlett-Packard Journal, Vol. 29, no. 3, November 1977, p. 6.

#### Li el el fr fr 19 fr 40 ve A d

#### Lawrence A. Stark

Larry Stark received his BSc degree in electrical engineering from the Massachusetts Institute of Technology in 1965 and his MSc and PhD degrees from Cornell University, the latter in 1971. He came to HP in 1979 after two years as an associate professor at Carleton University, Ottawa and six years in microwave components R&D. At HP's Stanford Park Division, he was a development engineer for the 8673A Synthesized Signal Generator and is now a product marketing engineer. A member of the IEEE, he has coauthored seven papers on microwave devices

and systems. Larry was born in Newton, Kansas and now lives in Palo Alto, California. He's married, has a daughter, and enjoys tennis, skiing, playing piano, and photography. He also enjoys planning landscaping projects which he'll get around to "one of these days."

#### **Ronald K. Larson**

With HP since 1972, Ron Larson has designed the 11720A Pulse Modulator and the output sections of several microwave synthesizers, including the 8673A. His pulse injection system for the 8673A is the subject of a pending patent. A native of Minneapolis, he served ten years as an electronic technician in the U.S. Navy, attaining the rank of Chief Petty Officer, then worked as an electronic technician for two more years before returning to school. He received his BSEE degree from the University of Minnisota in 1972. Ron is a guitar player, a karate student, a small

boat sailor, and a backpacker. He's married, has a son, and lives in San Jose, California.

# Compact Digital Cassette Drive for Low-Cost Mass Storage

This portable battery-operated unit uses minicassettes to store programs and data inexpensively for HP-IL systems.

by William A. Buskirk, Charles W. Gilson, and David J. Shelley

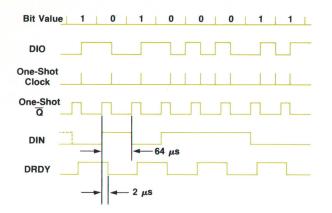

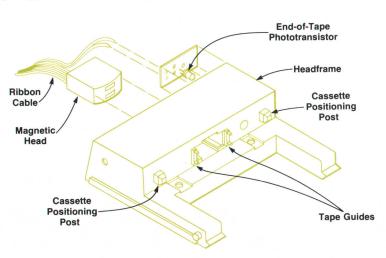

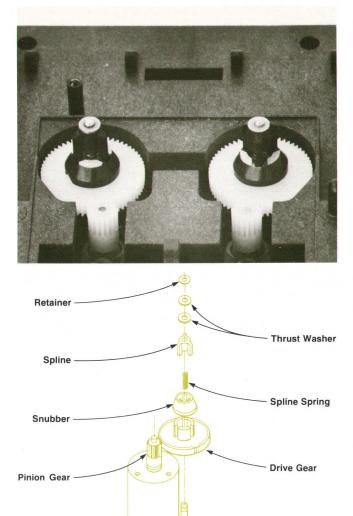

HE HP 82161A Digital Cassette Drive (Fig. 1) is a portable, programmable, mass storage peripheral for the Hewlett-Packard Interface Loop (HP-IL).<sup>1</sup> The storage medium is a removable minicassette that can store up to 128K bytes of information. Portability is achieved by the use of a four-cell nickel-cadmium battery pack, recharger, and power supply system similar to that used in other portable HP products. The 82161A is styled to fit in a family of compact peripheral devices such as the 82143A and 82162A Printer/Plotters, and to fit nicely in a system controlled by an HP-41 Handheld Computer or an HP-75 Portable Computer. The 82161A makes use of much of the package design of the 82143A Printer/Plotter,<sup>2</sup> producing a unit 178 mm wide by 133 mm deep by 57 mm high. Replacing the 82143A's printer mechanism on the top right side is a transport mechanism with a **REWIND** key and a door **OPEN** key located in front. To the left of these keys is the power switch and indicators POWER, LOW BATTERY, and BUSY. The top left side of the package offers a compartment to store two minicassettes. The two HP-IL cables and the recharger cable are connected to the 82161A via plug receptacles on its back panel.

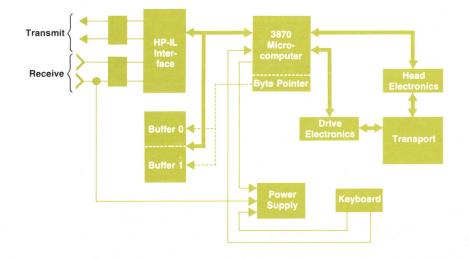

#### **Electronic System**

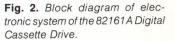

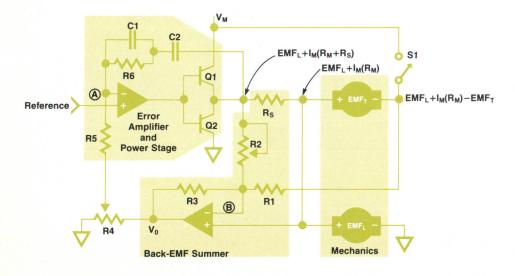

Fig. 2 is a block diagram of the electronic system of the 82161A. An internal microcomputer controls the head and motor drive electronics for the transport assembly and interacts with the HP-IL interface logic and data buffers.

The criteria for microcomputer selection for the 82161A included low cost, ready availability, low power consumption, and adequate I/O. To limit the number of electrical parts in the 82161A, a microcomputer that also contained ROM, RAM, and a timer, and could generate the encoded bit timing during a write operation was needed. A 3870 microcomputer with 2K bytes of ROM and 64 bytes of RAM was selected.

The logical interface of the 82161A is a generalized mass storage driver that provides the capability to execute operations such as initializing the tape, seeking a record, reading or writing a record, and rewinding the tape (see Table I).

**Fig. 1.** The HP 82161A Digital Cassette Drive is a compact battery-operated mass-storage unit designed for use in portable HP-IL systems.

|           |         | Table I  |       |          |

|-----------|---------|----------|-------|----------|

| HP 82161A | Digital | Cassette | Drive | Commands |

| DDL0  | Write buffer 0     | DDT0 | Read buffer 0       |

|-------|--------------------|------|---------------------|

| DDL1  | Write buffer 1     | DDT1 | Read buffer 2       |

| DDL2  | Write              | DDT2 | Read                |

| DDL3  | Set byte pointer   | DDT3 | Read address        |

| DDL4  | Seek               | DDT4 | Exchange buffers    |

| DDL5  | Format             | DDT5 | Transfer buffer 0→1 |

| DDL6  | Partial write      |      |                     |

| DDL7  | Rewind             |      |                     |

| DDL8  | Close record       |      |                     |

| DDL9  | Transfer buffer 0– | →1   |                     |

| DDL10 | Exchange buffers   |      |                     |

|       |                    |      |                     |

Buffer space for two 256-byte records of data is provided. Buffer 0 is used for data transfers between the HP-IL and the minicassette tape, and buffer 1 can be used by the HP-IL controller as virtual memory. The intent is to provide space to store a page of the tape directory and thereby reduce the number of seeks to the directory at the beginning of the tape. The DDL3 (set byte pointer), DDL8 (close record), and DDL6 (partial write) commands allow a memory-limited controller such as the HP-41 Handheld Computer to modify parts of a record without having to buffer the entire record in its mainframe. The record is read into buffer 0, modified, and written back to the tape with only the modification information passing around the HP-IL.

The ability to use the 82161A for extended remote data gathering tasks has been enhanced by the addition of the power-up/down commands. When the power switch on the front-panel keyboard is in the **STANDBY** position and a loop-power-down (PWRDN) command is received, the drive's power supply is turned off. When the HP-IL controller requires the loop to be active again, it sends a string of identify message frames, which turns the drive's power supply back on.

#### Software

The 2K bytes of machine code in the ROM of the microcomputer can be divided into three major areas: the power-on idle routine, the HP-IL routine, and the device control routines. The power-on idle routine, which uses approximately 160 bytes of code, sets up the initial state of the 82161A at power on and then alternates between testing for a cassette to be inserted into the drive, the **REWIND** key to be pressed, and calling the HP-IL routine. This routine also executes the device-clear and power-down functions. If either command is received, the HP-IL routine flags that fact and the drive responds after it finishes its latest task and returns to the idle routine loop.

The HP-IL routine, which takes approximately 460 bytes, provides the 82161A with basic talker and listener capabilities. This routine takes care of all communication with the HP-IL interface chip and passes all necessary information to the device control routines, primarily through a set of flag registers and one data register. This polled solution to HP-IL, in contrast to an interrupt-driven solution, is required because most of the device control routines need exclusive use of the microcomputer and can only give up control at specific times.

The device control routines, which take the remaining 1420 bytes of ROM, can be further divided. One part is the command decode portion. The device control is done with device-dependent commands (DDCs). When the HP-IL routine receives a DDC that it decides is of interest to the 82161A, it passes the DDC on to the command decode routine. Either the command is executed immediately, as in the case of a read or exchange buffer operation, or flags are set to control future actions, such as write and set byte pointer where the flags control where data bytes are put. A one-byte command buffer is used to hold a DDC received when the drive is busy. The HP-IL ready-for-command (RFC) message frame following this command is not retransmitted until the present task has been completed and the new command has been decoded.

The DDL5 (format) command initializes the record positions on the tape by recording all 512 records on both tracks. Each record contains a sync byte, a byte for the record number, a second sync byte, 256 bytes of data (each data byte initialized to 255), a checksum, and a final sync byte. Only during initialization is the first sync byte and the record number written. In all following write operations, the record number is read before the remaining part of the

**Fig. 3.** Timing diagram for signal lines and one-shot multivibrator states used to decode bit values stored on the 82161A tape cassette.

record is written. This serves two purposes. The first is to verify that the proper record is being written and the second is to fix the record position on the tape so that it does not move along the tape when it is overwritten.

The major criterion in selecting an encoding method for the 82161A was reliability. The tape drive system requires that the method have a large speed-variation tolerance and use a microcomputer to generate the encoded bit stream during a write operation. The tape lengths required to record a one and a zero should be the same so that the length of a record does not depend on the ratio of ones to zeros within the record. Also, the code should be self-clocking for easy decoding.

The method best qualified is the biphase-level or Manchester code. The rules of this code are 1) there is always a transition in a bit cell center, and its direction specifies the value of the bit, and 2) there is a transition on a bit cell edge only when the two bits on either side have the same value (see Fig. 3).

In a write operation, the time between transitions, bit cell midpoint to bit cell edge, is 64  $\mu$ s. During this time the transport status (stall, cassette present, and end of tape) is checked, the next nibble is read from the buffer and added to the checksum, and the next transition is calculated. The bit stream generated is sent to the sense amplifier on the DIO line.

There are two signals used in a read operation, DIN (data in) and DRDY (data ready). DRDY is the extracted clock and DIN is the latched data derived from the signal read from the tape. The microcomputer reads DIN and DRDY simultaneously and checks for DRDY to change state. When it does, the value of DIN is shifted into the register building the data. While it is in the read loop, the microcomputer also checks the transport status, stores the complete nibbles in the buffer, adds them to the checksum, and maintains a counter to detect when signal dropouts occur.

When the read/write routine is entered, the motors are turned on, the record number is read and verified, and the data portion of the record is then read or written. If a record number error and/or (in the case of a read) a checksum error is detected, the drive attempts the read or write operation a second time. If the microcomputer still detects an error, it stops the drive and reports the error to the HP-IL controller. Seek operations are always attempted in a relative manner first. When the new record number is received, it is checked to see if it is in range (i.e., <512), and the difference between the present position and the desired position is calculated. The transport is turned on to move in the appropriate direction, and by watching the DRDY line, the microcomputer counts interrecord gaps until the transport reaches the record immediately before the desired record. This record is read, and the record number is checked. If it is correct, the transport is stopped with the desired record next. If an error is detected, the tape is rewound, and the seek is attempted again, but this time from the beginning of the tape. This gives four chances of reading the record correctly and ensures accurate seeks.

#### **Data Storage and Retrieval**

The microcomputer handles digital information to and from the read/write electronics on a bit-by-bit basis using three data-related lines (DIN, DIO, and DRDY, see Fig. 3) and two control lines (REC and TRK). DIO is a bidirectional data line whose transfer direction is controlled by the state of the REC line. In the read mode (REC low), DIO is driven by the sense amplifier, while in the write mode (REC high), the sense amplifier goes into a high-impedance state and DIO is driven directly by the microcomputer. Both DIN and DRDY are generated by the decoder circuitry and are derived solely from DIO level changes. The TRK line is driven by the microcomputer to select which tape track (0 or 1) is read from or written to.

The sense amplifier is a custom bipolar integrated circuit. It contains the signal conditioning and logic circuits to drive the magnetic head during a write operation and to translate the low-level analog signals at the head to timerelated digital signals at DIO during a read operation.

Writing to the tape is accomplished by controlling the current flowing through the windings of the magnetic head. These currents produce a magnetic field across the gap at the front of the head. Three wires (two ends and a center tap) are attached to each winding (track) on the head. During a write operation, the center tap is connected to a constantcurrent sink, and each end of the winding is alternately driven high to control the direction of the current and thus the polarity of the magnetic field at the gap. The use of a current sink allows maximum rate of change of current, yet limits the peak direct current to 150% of that required to completely magnetize the tape.

During a read operation, the voltage at the terminals of the head is proportional to the rate of change of the magnetic flux across its gap and reaches a peak value when the gap is directly opposite a flux reversal on the tape. To decode recorded information properly, a digital signal with level changes corresponding in time to these voltage peaks must be generated. The sense amplifier generates this signal by amplifying and then differentiating the analog signal from the head. A zero crossing at the output of the differentiator corresponds to a peak of the amplified signal and is used to clock DIO level changes. The DIO level (high or low) is related to the polarity of the amplified signal at clock time and indicates the direction of the flux transition. Hysteresis is included to provide protection from unwanted transitions caused by electrical noise. Data content is encoded by the direction of the DIO level transition at the midpoint of a bit cell. Transitions at bit cell edges are used only as required to set up DIO for the proper change at the next midpoint (see Fig. 3). The decoder hardware ignores these edge transitions and provides the microcomputer with two signals—DRDY and DIN. A change at DRDY notifies the microcomputer that the signal at DIN represents valid data.

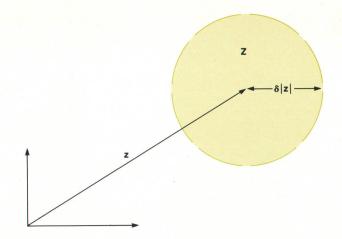

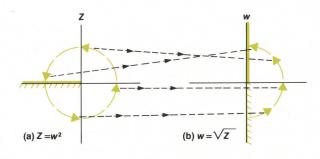

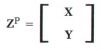

For every DIO transition a 100-ns pulse is generated and appears at the trigger input of a nonretriggerable one-shot multivibrator. The timing period of the one-shot multivibrator is set so that, if triggered by a midcell transition, the next edge transition, when it exists, will occur during the cycle and thus be ignored. When the timing cycle expires, the level of DIO, which corresponds to the encoded bit value, is latched into the DIN flip-flop. Approximately 2  $\mu$ s later, the output of the DRDY flip-flop changes, notifying the microcomputer that data is valid (see Fig. 3).